|

IBM리서치 연합이 이번에 개발한 5나노 기술은 지난 2015년 7월 공개한 7나노공정의 후속 기술로 작년에 상용화한 10나노 공정보다 두 세대 앞선 기술이다. 이 공정은 손톱만한 크기의 트랜지스터 300억개를 집적할 수 있어 7나노(200억 개)보다 집적 능력이 50% 향상됐다.

IBM리서치 연합은 10나노 칩과 비교하면 같은 전력에서 성능이 40% 향상되고, 전력 소모량은 동일 성능 대비 75% 감소할 것이라고 설명했다. 이로 인해 스마트폰 등 모바일 기기의 배터리 지속 시간이 지금보다 최대 2∼3배로 늘어날 수 있다고 덧붙였다.

이번 기술 개발로 저전력·고성능 칩이 보급되면 클라우드 서버를 통한 인공지능(AI) 등 인지 컴퓨팅(cognitive computing)과 사물인터넷(IoT) 등 데이터 집약적 어플리케이션의 성능 향상 및 기술 발전이 가속화될 전망이다.

IBM리서치 연합은 5나노칩 생산 일정에 대해선 구체적으로 발표하지 않았다. 현재 파운드리(반도체위탁생산) 업계 1위인 대만 TMSC가 이르면 올 연말 7나노 공정 생산에 들어갈 것으로 예상되고 있다. 또 삼성전자는 내년에 7나노, 2019년에 6·5나노에 이어 2020년 4나노 공정에 돌입할 계획이다.

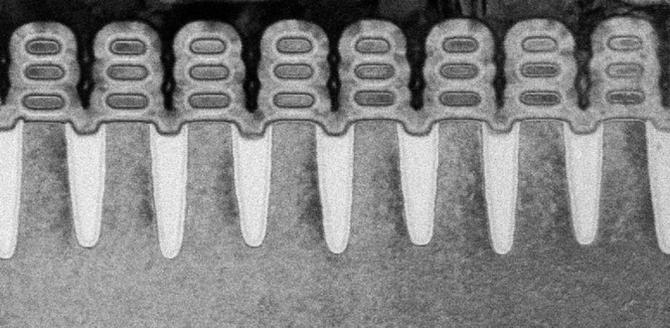

한편 이번 공정 개발은 IBM이 지난 2014년에 발표한 반도체 투자 계획에 따른 것이다. IBM은 당시 향후 5년간 30억 달러(3조 4000억 원)를 반도체 분야에 투자하겠고 로드맵을 밝혔었다. 개발팀은 기존 핀펫(FinFET) 아키텍처 대신 실리콘 나노시트 스택(여러 개 나노층을 쌓은 방식)을 사용한 트랜지스터 디바이스 구조를 만들었다. 핀펫 구조는 기존 평면(2D) 구조의 한계를 극복하기 위해 도입된 입체(3D) 구조의 공정 기술로 형태가 물고기 지느러미(fin)와 비슷해 이름 붙여졌다.

![[포토] 조사 마친 윤석열 대통령](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011501678t.jpg)

![[포토] 코스피, 코스닥 내림세...](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011501243t.jpg)

![[포토]'내란 우두머리 피의자' 윤석열 대통령 공수처로 이동](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011501058t.jpg)

![[포토] 네스프레소 2025 캠페인 론칭 토크쇼](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011501014t.jpg)

![[포토] '와일드무어' 미디어 행사](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011501005t.jpg)

![[포토]공수처 차고로 들어가는 윤 대통령 차량](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011500861t.jpg)

![[포토]사다리로 차벽 넘는 공수처](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011500701t.jpg)

![[포토]공개된 팰리세이드 풀체인지](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011500422t.jpg)

![[포토]공공기관 채용정보박람회 개최…“신규채용 2만4000명 추진”](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011400899t.jpg)

![[포토] 설 명절 자금 방출](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011400672t.jpg)

![[포토]박현경,백여 명의 팬들과 즐거운 출정식 개최](https://spnimage.edaily.co.kr/images/vision/files/NP/S/2025/01/PS25011200149h.jpg)

![[단독]尹 16일 헌재 출석하려 했다…"변론권 보장 못받게 돼"](https://image.edaily.co.kr/images/vision/files/NP/S/2025/01/PS25011501489h.jpg)