[이데일리 강민구 기자] 우리나라 연구진이 일본 기술 대비 95% 전력을 덜 쓰고, 생산라인을 줄이는데 필요한 반도체 패키징 기술을 개발했다. 대만반도체제조회사(TSMC), 인텔, 삼성전자 등 글로벌 반도체 파운드리 회사와 기술에 대한 공정성, 신뢰성을 평가하고 있다. 앞으로 ‘우수’ 평가를 받으면 3년 내 상용화해 자율주행차, 데이터센터에 필요한 AI반도체를 생산할 수 있을 것으로 기대를 모은다.

한국전자통신연구원(ETRI)은 나노 소재기술을 이용해 반도체 공정에 꼭 필요한 신소재를 개발했다. 일본이 보유한 기술 대비 95% 전력을 줄일 수 있는 반도체 조각 칩(칩렛) 패키징 기술이다.

최광성 ETRI 저탄소집적기술창의연구실장은 “반도체 패키징과 마이크로 LED 디스플레이 분야는 40~50년 동안 일본 소재와 장비 기술에 대한 의존도가 컸다”며 “기술 격차가 커서 자립화가 쉽지 않은 상황이었는데 일본을 따라가던 방식에서 벗어났다는 부분이 의미가 있다”고 했다.

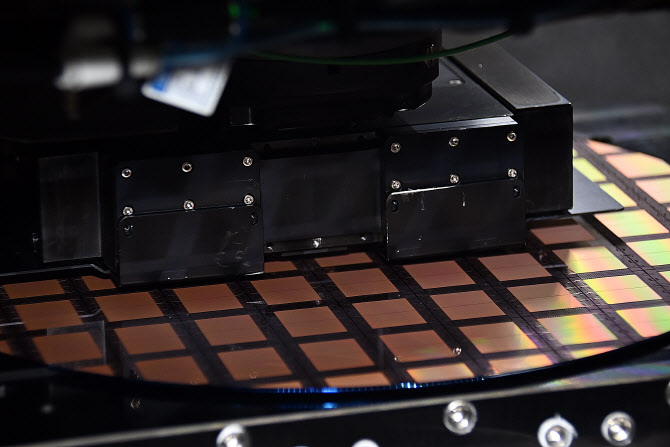

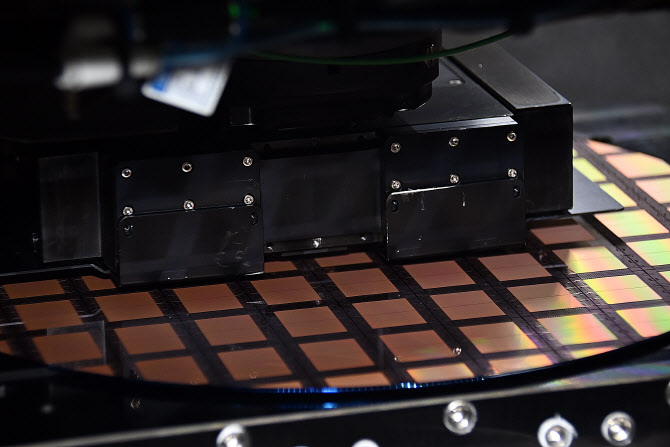

| | 면 레이저를 통한 칩렛 칩적 공정 모습.(사진=ETRI) |

|

비전도성 필름 붙이고 레이저 이용

그동안 반도체 업계에서는 첨단 반도체 패키징 공정에 주로 일본 소재를 사용해왔다. 세척, 건조, 플라즈마 등 9단계 공정을 거쳐야해 복잡하고 다양한 장비를 써야 했다. 전력소모가 크고 유해물질도 배출했다.

ETRI 연구팀은 반도체 웨이퍼 기판에 개발한 신소재인 비전도성 필름을 붙인 후 타일처럼 생긴 칩렛에 1초 정도 면 레이저를 쏴서 가볍게 만드는 공정을 이용했다. 핵심 신소재는 고분자 필름으로 만들었다. 10~20마이크로미터 두께의 에폭시 계열 소재에 환원제를 넣은 나노소재로 만들었다. 이 소재에 레이저를 쏘면 반도체 후공정(패키징) 단계에서 세척, 건조, 도포, 경화 등에 이르는 단계를 줄이는 방식이다.

공정이 간단해 전체 생산라인을 기존 20미터 이상을 4미터로 줄일 수 있다. 공정에 쓰던 질소 가스도 필요 없어 유해물질이 발생하지 않다. 상온에서도 집적 공정이 가능하다.

연구팀은 반도체, 디스플레이 업체에 필요한 저전력·친환경 반도체 공법에 활용될 수 있다고 기대했다. 첨단 칩렛 집적, 마이크로 LED 공정에도 적용할 계획이다.

이일민 ETRI 창의원천연구본부장은 “최근 ESG 경영이 반도체, 디스플레이 업계의 화두”라며 “산업계에 친화적인 저전력 신공법을 누가 먼저 개발하느냐가 사활이 걸린 문제로 이번 기술이 파급효과가 있다”고 했다.

![[포토] 광화문광장 나눔온도 70.5도](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122600729t.jpg)

![[포토]조중석 이스타항공 대표-고토다 도쿠시마현지사 인사](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122600693t.jpg)

![[포토]여야 합의 강조하는 한덕수](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122600665t.jpg)

![[포토]김용현 전 국방부 장관 변호인단 기자회견 열어](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122600563t.jpg)

![[포토]윤이나,밝은 모습 인터뷰 시간](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122600087t.jpg)

![[포토]명동성당 성탄 대축일 미사](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122500276t.jpg)

![[포토]다시 돌아온 있지 리아](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122500136t.jpg)

![[포토]크리스마스엔 스케이트](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122500245t.jpg)

![[포토]37번째 거리 성탄예배 열려 방한복·도시락으로 사랑 나눔](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122500231t.jpg)

![[포토]조국혁신당 공수처 앞에서 기자회견](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/12/PS24122500219t.jpg)

![[포토]윤이나,후배 양성을 위해 2억원 기부했어요](https://spnimage.edaily.co.kr/images/vision/files/NP/S/2024/12/PS24122600088h.jpg)