|

[이데일리 신하영 기자] 아주대 연구진이 반도체 공정 혁신을 견인할 메커니즘을 규명했다. 한계에 도달한 반도체 미세화·다층화 기술에 새로운 해결책으로 활용될 전망이다.

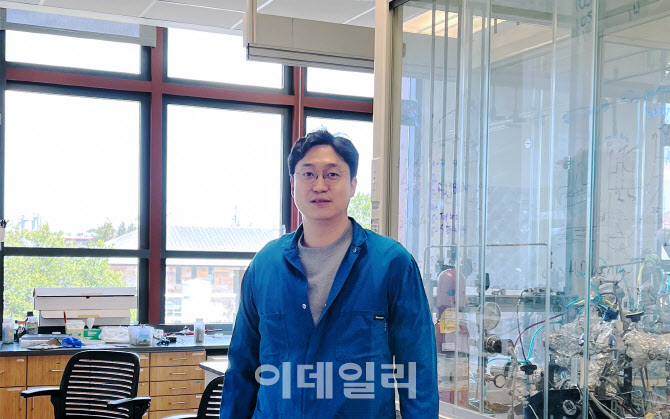

아주대는 오일권(사진) 전자공학과 교수가 이러한 연구성과를 얻었다고 17일 밝혔다. 이번 연구는 한국연구재단 기초연구실사업의 지원을 받아 수행됐으며, 연구결과는 미국 화학분야 권위지(Journal of the American Chemical Society) 7월 6일자 표지논문으로 게재됐다.

이번 연구는 현재 반도체 양산에 적용된 공정 기술 중 하나인 ‘원자층 증착법’의 세부 메커니즘에 대한 의문에서 시작됐다. ‘원자층 증착법’이란 분자들의 자기 제한 표면 반응(self-limiting)을 기반으로 박막을 원자 단위에서 고품질로 증착하는 방법이다. 원자층 증착법을 통해 매우 얇은 원자 단위 두께의 층을 실리콘 웨이퍼 같은 평평한 물질에 소자의 손상 없이 균일하게 증착할 수 있다.

오 교수는 이어 “반도체 전자 소자가 미세화됨에 따라, 반도체 소자의 특성은 박막뿐만이 아니라 분자층 표면 반응과 반응 케미컬의 특성에 영향을 받는 상황이 됐다”며 “이번 연구를 통해 표면 분자 반응 조절의 메커니즘을 밝힘으로써 앞으로 반도체 소자 제작에 있어 박막의 질과 특성 디자인에 활용할 수 있을 것으로 전망한다”고 말했다.

![[포토]박종준 처장, 특수공무집행방해 혐의로 경찰 출석](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25011000511t.jpg)

![[포토] 맘스홀릭베이비페어 전시](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010901108t.jpg)

![[포토]수도권 첫 한파주의보](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010901027t.jpg)

![[포토]'무죄'받고 이동하는 박정훈 전 수사단장](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010900998t.jpg)

![[포토]기자회견 하는 김상욱 의원](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010900987t.jpg)

![[포토]전국정당을 넘어 K-정당으로 향하는 더불어민주당](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010900948t.jpg)

![[포토]발언하는 권영세 위원장](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010900599t.jpg)

![[포토]포즈 취하는 팀테일러메이드](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010800134t.jpg)

![[포토]서울 올겨울 첫 한파특보… 내일 체감온도 영하 17도](https://image.edaily.co.kr/images/Photo/files/NP/S/2025/01/PS25010800820t.jpg)

![[포토]홍재경 아나운서,론칭쇼 진행합니다](https://spnimage.edaily.co.kr/images/vision/files/NP/S/2025/01/PS25010800229h.jpg)

![공중제비 도는 로봇개 “어메이징”…로봇 공습 나선 中[영상][CES2025]](https://image.edaily.co.kr/images/vision/files/NP/S/2025/01/PS25011000623b.jpg)